Simulaciones de Elementos Finitos ayudan a predecir la deformación en el empaquetado de dispositivos integrados

Los dispositivos integrados fabricados en semiconductores, incluyendo los circuitos electrónicos, las memorias y los sensores, están hechos de materiales cristalinos y frágiles. El encapsulado microelectrónico tiene la importante función de proporcionar interconexiones eléctricas con las placas de circuito impreso y proveer protección mecánica, térmica y química al dispositivo semiconductor. Durante este proceso de producción, los dispositivos integrados se montan y “encapsulan” dentro de una “carcasa” protectora, fabricada de capas de diferentes materiales, incluyendo resinas y otros polímeros. Estos materiales se encogen y deforman por efecto de la temperatura, generando acumulación de estrés y distorsión en los dispositivos, lo que puede reducir la productividad o, en casos extremos, destruir el producto.

Recientemente, investigadores del Grupo de Encapsulamiento Microelectrónico del Instituto de Investigación Eldorado, uno de los centros de Investigación y desarrollo más grandes de Brasil, realizaron un estudio sobre el proceso de encapsulamiento de dispositivos integrados. El grupo es parte del desarrollo de hardware y procesos del instituto, trabajando en el desarrollo y perfeccionando productos, trabajando con proyecto, ensayos y selección de materiales para mejorar la productividad y el rendimiento de los dispositivos integrados.

El trabajo, titulado “Model and Simulation of Warpage in Packaged IC Strips After Mold Array Process”, fue presentado en la conferencia WCAS 2020 – Workshop on Circuits and Systems Design, y premiado como mejor trabajo con énfasis industrial. La conferencia forma parte de Chip in the Fields 2020, una importante serie de congresos en el área de semiconductores, microelectrónica y dispositivos integrados.

Los investigadores Jose Luis Ramirez, Ricardo Yoshioka, Claudemir Coral, Carolina Nunes e Igor Namba estudiaron el proceso de deformación luego de aplicar resina protectora por proceso de moldeo, con el fin de sugerir una metodología de proyecto y selección de materiales, que se puede utilizar para predecir el comportamiento del dispositivo ya encapsulado, reduciendo el costo de creación de prototipos.

El estudio utilizó datos experimentales, modelos y simulaciones FEM

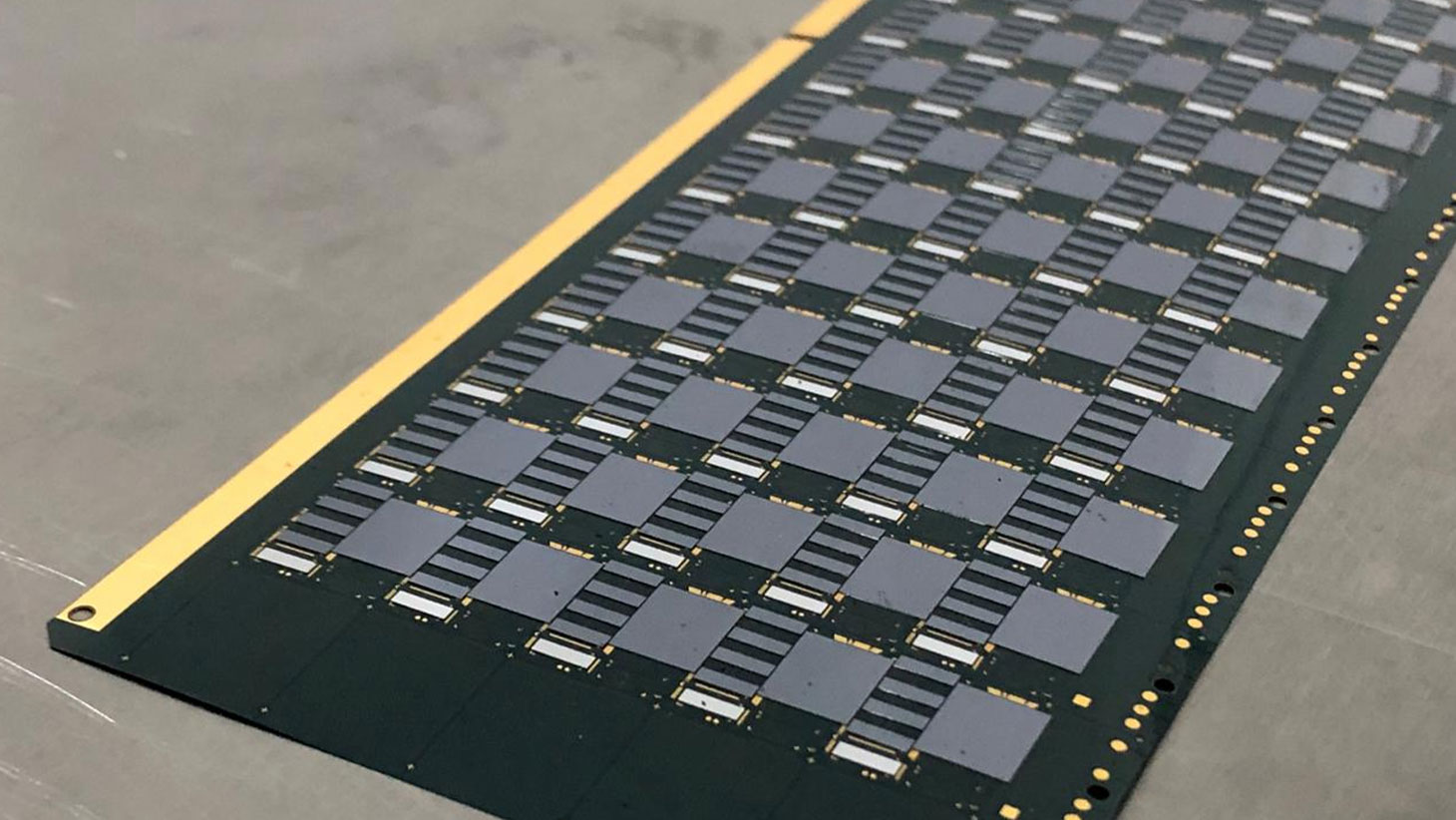

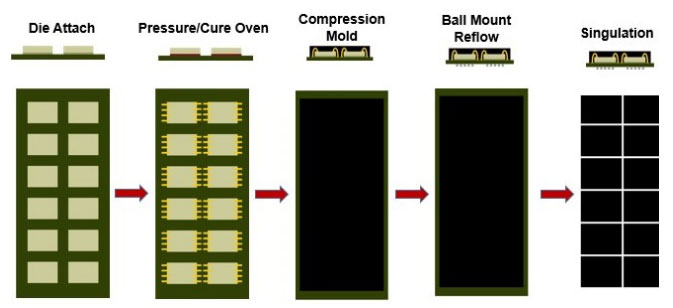

Existen varias tecnologías para el encapsulamiento, entre estas el proceso de moldeo matricial de componentes BGA (Mold Array Process MAP-BGA), donde resina es aplicada sobre los dispositivos usando un molde y presión. Este proceso es muy utilizado en la industria para aumentar la productividad, ya que se encapsulan varios dispositivos al mismo tiempo. El proceso se puede resumir de esta manera: se montan múltiples dispositivos a una placa usando una película adhesiva (Die Attach Film -DAF), se realizan interconexiones eléctricas, una resina epoxi cubre los chips de silicio, se colocan bolas de soldadura y se separan los dispositivos, como se ilustra en la figura abajo.

Proceso MAP-BGA: Fijación de los dispositivos en una matriz sobre el sustrato => Curado DAF – Conexión de dispositivos usando líneas de oro => Molde por compresión => montaje de bolas de estaño => Corte e individualización cada dispositivo

Cada uno de estos procesos requiere diferentes temperaturas. La diferencia de expansión entre las capas genera tensiones residuales y deformaciones no deseadas, que finalmente resultan en distorsiones. En casos extremos, la tensión puede provocar grietas o delaminación, provocando fallas en el dispositivo, pero incluso una tensión relativamente pequeña puede provocar la distorsión de la pieza moldeada. La resina usada representa la mayor parte del volumen del dispositivo encapsulado y, por lo tanto, juega un papel clave en el comportamiento mecánico y la deformación del conjunto.

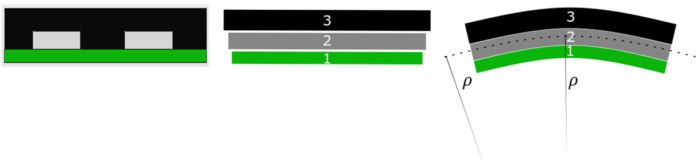

Representación de “warping” en dispositivos encapsulado, modelando el componente en varias capas coladas, cada una con una expansión térmica diferente.

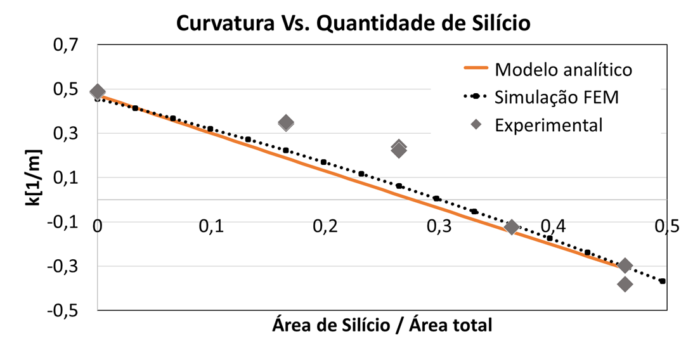

Con el fin de crear un modelo simplificado para predecir la disposición, los investigadores desarrollaron una ecuación analítica para describir la curvatura basada en la deformación en cada una de las capas, relacionando la curvatura con diferentes variables de diseño (como el espesor de la capa de resina y la cantidad de silicio en cada dispositivo). Para observar y mejorar el modelo analítico se utilizó el Método de Elementos Finitos (FEM) y las herramientas de simulación Ansys. Este análisis permitió simular el encapsulamiento para diferentes valores de las variables elegidas.

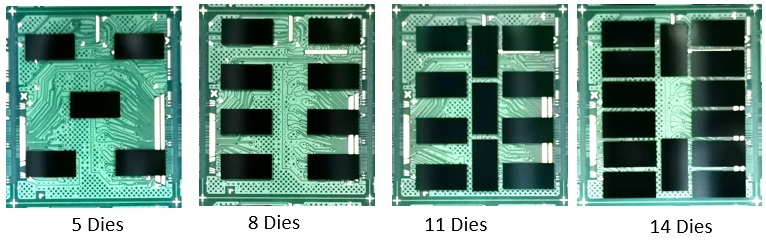

Especímenes usados en los experimentos con diferentes números de chips de silicio.

Se utilizó una metodología experimental para validar el modelo, utilizando dispositivos con diferentes cantidades de resina o número diferente de circuitos. Los resultados experimentales y de simulación validaron el modelo analítico.

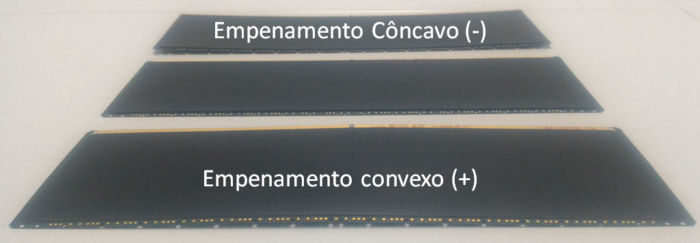

Ejemplos de matrices después del proceso de encapsulamiento con diferentes deformaciones.

Las herramientas de simulación validan el modelo para encapsulamiento de los dispositivos integrados

La investigación utilizó la herramienta de simulación Ansys Mechanical para analizar la estructura, lo que permitió observar el comportamiento de esfuerzos y deformaciones relacionados con las variaciones de temperatura. La simulación permitió no solo reproducir los resultados experimentales, sino también expandir los análisis a otros escenarios donde hubiera sido difícil o costoso fabricar prototipos.

Simulación de tensiones y deformaciones en el proceso de molde. A medida que disminuye la temperatura, se induce estrés térmico. Cuando se extrae el dispositivo del molde, aparece distorsión.

Se construyó un modelo detallado en elementos finitos del dispositivo empaquetado con Ansys Mechanical. El modelo simuló el comportamiento del material sólido, considerando el molde parcialmente curado y completamente solidificado. Si bien en el modelo analítico todas las capas se simplifican y se consideran homogéneas, fue posible considerar todos los detalles y materiales en la simulación.

Según Jose Luis Ramirez, Ingeniero de Desarrollo de Hardware en el Instituto Eldorado, «Las herramientas de simulación de Ansys fueron especialmente útiles para comprender el comportamiento de las tensiones y deformaciones mecánicas en procesos con variaciones de temperatura». Se observó un comportamiento muy cercano entre el modelo analítico y el resultado de la simulación FEM. Aún más relevante, los datos experimentales se ajustan al comportamiento esperado predicho por la ecuación y las simulaciones.

Curvatura para diferentes espesores de resina, FEM y experimental.

Curvatura para diferentes cantidades de silicio en los modelos analítico, FEM y experimental.

El modelo desarrollado en la investigación permite predecir la distorsión y curvatura final del dispositivo según el espesor y las propiedades del material utilizado y, de esta forma, mejorar la selección de los parámetros del proceso sin necesidad de fabricar diferentes prototipos.